V.Priyanka Brahmaiah<sup>1</sup>, Anudeep Peddi<sup>2</sup>, R. Saichandan<sup>3</sup>

Turkish Online Journal of Qualitative Inquiry (TOJQI) Volume 12, Issue5, May, 3579- 3592

#### **Research Article**

## Fpga Implementation Of 4-Bit Alu Using Reversible Logic Gates

V.Priyanka Brahmaiah<sup>1</sup>, Anudeep Peddi<sup>2</sup>, R. Saichandan<sup>3</sup>

#### Abstract

The adders, multipliers are the essential building blocks for every integrated circuit (IC). Thus, the design of adders and multipliers must inhibit the area, delay and power efficient properties. But most of the CMOS based logic gates arefailed to provide these properties in adders, multipliers implementation. To solve this problem reversible logic gates has been developed at nano technology level using the quantum dot cellular automata properties. The quantum cost for this reversible logic gates very low, thus in this paper reversible logic gates-based 4-bit adder, 4-bit subtractor, 4-bit multiplier and 4- bit ALU developed with reconfigurable properties. The effective utilization of these gates provides more flexible nature for ICs. The implementations are conducted in Xilinx ISE environment, the simulation results shows that proposed method is area, power and delay efficient compared to the conventional approaches.

Keywords: Reversible Logic Gates, RippleCarry Adder, Array Multiplier.

#### INTRODUCTION

The digital computer performs operations that seem to discard data in computer's history. In this, the machine state will be ambiguous [1]. The operations of computers incorporated to overwrite/erase the data and also consists a section which addresses a bit of data addressed at distinctive transfer instructions. Hence, the system is logically irreversible - its transition work lacks a single-esteemed inverse [2]. In development of nanotechnology, which is speed enhanced, less sized, and composed of highly convoluted engineering design than existing systems. The improvement in the technology has introduced

a system considering the parameters like power and heat dissipation and clock frequency [3].The highly enhancement in the clock frequency to get the better speed and increase the total transistors stuffed in a chip to accomplish required system results more power consumption. Almost in all the total logic gates for logical operations in old computer are irreversible. Hence, in every time a logical operation is performed to know input lost and it is dissipated as heat. For any digital design, the power loss must be considered for desired parameter [4]. The current technology improvement in the computer design are increased and also the power utilization also optimized by using the Reversible

<sup>&</sup>lt;sup>1</sup>Assistant Professor, Department Of ECE, VNR Vignana Jyothi Institute of Engineering and Technology, Hyderabad

<sup>&</sup>lt;sup>2</sup>Assistant Professor, Department Of ECE, VNR Vignana Jyothi Institute of Engineering and Technology, Hyderabad

<sup>&</sup>lt;sup>3</sup>M. TECH STUDENT, Department Of ECE, VNR Vignana Jyothi Engineering and Technology, Hyderabad

logic (RL). As per literature with exponential development of heat produced because of information loss is major issue. The heat dissipation causes the reduction in the circuit"s execution time and lifetime. Thus, the use of reversibility can give low power consumption and heat dissipation system. In the work of literature indicated how the reversibility can be achieved with zero power dissipation. Also, reversibility cannot cause information loss as like in irreversible. For reversibility circuit design we need set of reversible gates (RGs) and these kind of gates are available since last decades. As per literature [7] focused on logical irreversibility which causes more heat losses. Accordingly, a computer must dissipate entropy (kTln 2) of energy for each data loss. An irreversible computer can made reversible by conserving the information. The reversible machine additional unit is used to store the every operation performed. In this machine the controls both the input and output information. Thus, as discussed in [7], this will prevent the information loss as it can be reused. Thus reversible computer halts the information, can be erased in middle results, the output can be reused as input. The research starts with the concept of reversibility [7] where at the ending of computation and first inverse of the transition work, the system can perform reverse computation. The Reversible circuit (RC) can create output from every input, i.e., there is a coordinated corresponding to input and output vectors. Thus, in a RC outputs will be equal to inputs. A circuit can be "reversible", when the input vector is uniquely recouped by output vector corresponding to input and output unit. The RL is a promising design paradigm offers efficient to design the computers with powerdissipation. The RL can system. improve the standard of computing The reversible processing fundamentals are the relationship among entropy, heat transfer in a system. The RL guidelines the objective (reversible) device with equal lines of input and output delivering a processing domain. The work of Yugandhar, K., et al [8] gives a new design method for array multiplier which uses more garbage outputs. Authors considered the 4-bit reversible high performance array multiplier (RHPAM) with reversible high-performance adder (RHPA) synthesizing by utilizing the advanced bi-directional synthesis mechanism. Hence, for multiplier synthesis, the optimization of input bits and also the delay are not yet addressed except in therecent works which discusses about the post synthesis mechanism to reduce the quantum bits in the reversible multiplier.

Kamaraj, A., and P. Marichamy [9] introduced the fault tolerant ALU (FTALU) with no input carry with one ancillary input bit. Authors have examined new QR carry adder designs with no ancillary input bit gives improved delay. The reversible ALU in the existing literature is evaluated by garbage outputs, total RL used, QC and delay.

Amirthalakshmi, T. M., and S. Selvakumar Raja [10] have described concepts of 8-bit Reversible ALU (RALU). Also, designed and implemented high cost, efficient, fault tolerant, reversible ALU. In this more garbage outputs were compensated with fewer operations. The author concluded that the ALU performs all the logical operations better than existing methods not arithmetic operations.

Table 1: Summary of Literature survey

| Authors | Problem   | Outcome |

|---------|-----------|---------|

|         | addressed |         |

| Yugandhar, K[8]               | Synthesis          | ofALU design with Low |

|-------------------------------|--------------------|-----------------------|

|                               | reversible gate    | s,QC, delay and       |

|                               | Adder and multipli | ergarbageoutput       |

|                               | design             |                       |

|                               | issues             |                       |

| Kamaraj, A., and              | RL design Reduce   | edReduced minimum     |

| P. Marichamy[9]               | minimum            | outputs               |

|                               | outputs            |                       |

| Amirthalakshmi,               | Reversible desig   | nBetter design than   |

| T. M., and S. Selvakumar Raja | with sequential    | traditional RL design |

| [10]                          | circuits           |                       |

To solve these problems, the paper is contributed as follows

A novel full adder is designed with fredkingate and Feynman gate combinations; this reduces the delay and area requirement.

An N-bit reversible RCA has developed utilizing the reversible fulladder.

An N-bit reversible array multiplier has been developed by utilizing the fredkin gates and N-bit reversible RCA.

An N-bit Reversible adder subtractor was designed; using this adder subtractor and array multiplier an N- bit Reversible ALU was developed.

A detailed analysis of results has been presented with comparison to the existing method .the results shows that proposed method is area, power and delay efficient.

Rest of the paper as follows: section 2gives the detailed analysis is over reversible logic gates with its unique properties also introduces operations of Feynman gate and Fredkin gate. Section 3gives the detailed analysis of reversible designs such as proposed Full adder, proposed N-bit RCA, proposed N-bit array multiplier, proposed N- bit adder subtractor and N-bit ALU. Section 4gives the detailed analysis on results with respect to both simulation and synthesis outcome and comparative analysis also performed with various convention approaches. Section 5deals about conclusionand future works of proposed methods.

## **REVERSIBLE LOGIC GATES**

Reversible logic gates are developed with the pass transistor technology using quantum dot cellular automata. The reversible logic gates are preferable to design the chips because they exhibit the following properties.

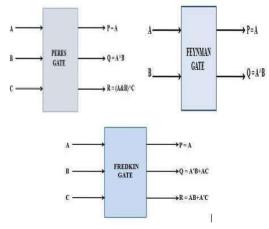

**FEYNMAN GATE:** Figure 1(a) gives the detailed operation of Feynman gate, it acts as both buffer and exclusive or gate.

**FREDKIN GATE:** Fredkin gate is a universal gate, any arithmetical and logical operation can be implemented very effectively with low area, delay and power consumption compared to basic gates. Thus it is effectively used in the ALU operation. The detailed structure of Fredkin Gatepresented in Figure 2(b).

The main applications of Fredkin gate is that, it acts as AND gate as well as OR gate by controlling the input pins. If C input of Fredkin gate is 1'b0, then R output of Fredkin gate acts as AND operation.

$C = 0 \longrightarrow R = A\&B + \overline{A\&1'b0} = A\&B(1)$

If B input of Fredkin gate is 1'b1, then R output of Fredkin gate acts as OR operation respectively.

$B = 1 \longrightarrow R = A\&(1'b1) + \overline{A}\&C = A + A\&C = A + C$ (2)

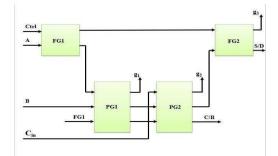

From the figure 2, it is observed that if Ctrl input is zero, the design acts as reversible Full adder. if Ctrl input is one, the design acts as reversible Full subtractor. And subtraction operation developed based on the twos compliment addition.

**PERES GATE:** Figure 1(c) gives the detailed operation of Peres gate, it acts as both buffer and exclusive or gate. If the input C is zero, then the outputs R acts as AND function respectively.

## PROPOSEDMETHOD

The ALU is the essential building block in every DSP processor DIP processor, Intel processors and all the types of integrated circuits. Thus, the efficient design of ALU makes the design to area, delay and power efficient. In the proposed method majorly focuses on design the 4-bit ALU with combinations of Feyman gate and Fredkin gate, The 4-bit ALU also utilizes the 4-bit Adder, 4-bit subtractor and 4-bit multiplier, thus the operation of each arithmetic unitexplained in detail.

PROPOSED REVERSIBLEFULLADDER-SUBTRACTOR

The design of Reversible full adder and subtractor (RFAS) will be effectively used for the purpose of ALU by utilizing the single architecture for both operations. the twos compliment addition.

$Ctrl = 0 \rightarrow out = A + B = A + B + Ctrl (3)$

$Ctrl = 1 \rightarrow out = A - B = A + B + 1 = A + B + Ctrl$  (4)

if ctrl is zero, Feynman gate Fg1 will results the Q output as input A. if ctrl is one, Feyman gate Fg1 will results the Q output as compliment of input A. in both cases, P output such as buffer of Ctrl applied to the A input of Feyman gate Fg2 and Q output applied toA input of pears gate PG1 respectively. Single pears gate is enough to implement half adder or half subtractor depending on it's a input and maintaining the C input to Zero. Now, PG1 outputs P1, Q1 will act as half adder sum, carry out when ctrl is zero and similarly act as half subtractor difference, borrow out when ctrl is one. Similarly, Now PG2 outputs P2, Q2 will act as Full adder sum, carry out when ctrl is zero and similarly act as Full subtractor

difference, borrow out when ctrl is one. But as stated above, the design is based on twos compliment methodology, so the final sum or difference contains

compliments so it must be controlled by Feyman Gate FG2.the Feyman Gate FG2contains the inputs as P output from FG1 and Q2 output from PG2. If control is zero, the resultant Q output is Sum and if control is one, the resultant Q output is difference respectively.

## **PROPOSED 4-BITREVERSIBLE ADDER-SUBTRACTOR**

Figure 3 shows the architecture of N-bit reversible adder-subtractor (RAS) consisting of Nnumber numbers of RFAS, it acts both N- bit reversible adder and N-bit reversible subtractor depending on the ctrl input.

Figure 3: architecture of N-bit RAS

As like RFAS, if ctrl is zero it acts as N- bitreversible adder and, if ctrl is one it acts as N-bit reversible subtractor respectively. The operation of N-bit RAS as follows,

**Step 1:** individual RFAS generates the sum and bits alone by considering the A, B as present inputs and CBin as carry or borrow out CBout from previous stage. If ctrl is zero, sum and carryout s will generate as final output. If ctrl is one difference and borrow outputs will generate as final output respectively.

**Step 2:** individual RFAS also generates the CBout, by applying the CBoutof present stage RFAS to CBinof next stage RFAS.

**Step 3:** by performing the step 1 and step2 operations for N number of stages will develop the N-bit RAS operation with low power, delay and area consumption.

Step 4: By making N as 4, it acts the 4-bit adder and subtractor.

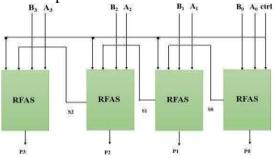

PROPOSED 4-BIT ARRAYMULTIPLIER

The multiplier is the essential building block in the DSP processor DIP processor, ALUs and all the types of integrated circuits. Thus the efficient design of multiplier makes the design to area, delay and power efficient.

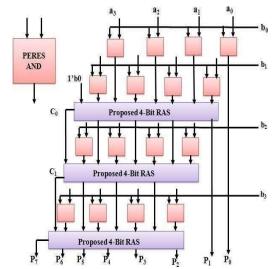

The figure 4 represents the N-bit Reversible array multiplier (R-AM) utilizing these Fredkin gates and N-bit RCA adders.

**Step 1:** every multiplier consists of partial products as fundamental outcomes. The partial products are generating by performing the bitwise AND operation between A inputs to the B inputs in a chronological order. Here, the PERES gate will be utilized to perform the AND operation as mentioned section 2. For implementing N-bit multiplier, we require

$N^2$  Number of AND operations so that of PERES Gates. After developing the partial products, the partial products are grouped together to perform the multiplication operation respectively.

Figure 4: Proposed Reversible 4-bit ArrayMultiplier

Figure 5: operation of R-AM **Step 2:** after developing the partial products,the partial products are groupedtogether to perform the multiplication operation respectively.

**Step 3:** Figure 5 shows the detailed analysis of partial products addition for 4-bit multiplier. For developing the 4-bit multiplier we require (4-1) number of adder with each of 4-bit

For first 4-bit RFAS(control input is zero so acts as adder) the input will be M1, M2 and Cin become zero, which generates S1 as its sum output and C0as its carry output.

## 3.3 PROPOSED N-BIT REVERSIBLEALU

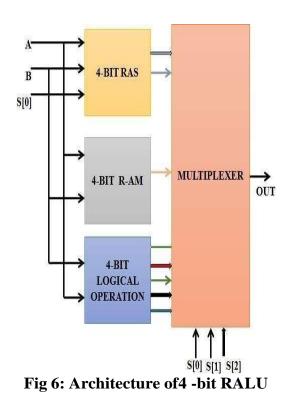

Fig 6 shows the proposed 4-bit Reversible ALU (RALU) which consist of 4-Bit RAS, 4- bit R-AM and 4-bit reversible logical operations. When selection lines of multiplexer are 3"b000, then control input for 4-Bit RAS becomes zero and multiplexer selects the adder output, if selection lines of multiplexer is 3"b001, then control input for

4-Bit RAS becomes one and multiplexer selects the subtractor output respectively. When selection lines of multiplexer are 3"b010, and then multiplexer selects the N- bit R-AM output such as multiplication. When selection lines of multiplexer is 3"b011 to 3,,b111, and then multiplexer selects outputs of Bit wise AND, OR, NAND, NOR XOR and XNOR operations generated using Fredkin and Peres gates correspondingly.

### **RESULTS AND DISCUSSIONS**

All the proposed designs have been programmed and designed using Xilinx ISE software this software tool provides the two categories of outputs named as simulation and synthesis. The simulation results give the detailed analysis of proposed design with respect to inputs, output byte level combinations. Through simulation analysis of accuracy of the addition, multiplication process estimated easily by applying the different combination inputs and by monitoring various outputs. Through the synthesis results the utilization of area with respect to the programmable logic blocks (PLBs), look up tables (LUT) will be achieved. And also time summary with respect to various path delays will be obtained and power summary generated using the static and dynamic powerconsumed.

| Name                          | Value                     | ions .                        | 20 ns                          | 40 ns                                   | Sons     | 80 ns                                |

|-------------------------------|---------------------------|-------------------------------|--------------------------------|-----------------------------------------|----------|--------------------------------------|

| ▶ 🧗 P[7:0]                    | 00010011                  | 00010111                      | x 00011100                     | 00010110                                | 00001101 | 8 00010011                           |

| 🕨 😽 A[3:0]                    | 0111                      | 1011                          | 1111                           | 1100                                    | 0101     | 0111                                 |

| ▶ 🖬 8[3:0]                    | 1100                      | ( 1100                        | 1101                           | 1010                                    | 1000     | 1100                                 |

| ▶ 🙀 S(2.0)                    | 000                       |                               |                                | 000                                     |          |                                      |

| ▶ 📢 N(31.0)                   | 0000000000000             |                               | 00                             | 100000000000000000000000000000000000000 | 000100   |                                      |

|                               | Fig                       | ure7:                         | Full A                         | dder o                                  | output   |                                      |

|                               |                           | -<br>N-Som                    |                                |                                         | -        | 100.000                              |

| lame                          |                           | ure7:                         | Full A                         | 140 rs                                  | Films    | 180 ms                               |

|                               | Value                     | tirs                          | 20 ns                          |                                         | Films    | 100.000                              |

| Name<br>10 17731              | Value<br>Doptosito        | lüns<br>( 0000000             | 20 ns                          | 40 ns<br>00000 100<br>1100              | 60 ns    | 80 ns                                |

| Name<br>• ₩ 1738<br>• ₩ А330] | Value<br>00000110<br>1100 | (0 ms<br>0 00000000<br>0 1100 | 20 ns<br>1 000000 10<br>1 1111 | 40 ns<br>00000 100<br>1100              | 60 ns    | 100.000<br>100 ms<br>100 110<br>1100 |

Figure8: Full Subtractor output

| Name                                                                       | Value                                    | Ons                           | 20 ns                                     | tôns                                    | 60 ns                                                   | (80 ns                      |

|----------------------------------------------------------------------------|------------------------------------------|-------------------------------|-------------------------------------------|-----------------------------------------|---------------------------------------------------------|-----------------------------|

| ▶ 👹 F(7:0)                                                                 | 01001000                                 | 10012000                      | 11000011                                  | 01100000                                | 01110000                                                | 01001000                    |

| A[R0]                                                                      | 1100                                     | 1100                          | X 1111                                    | 1100                                    | 1110                                                    | 1100                        |

| ► Nd 8(30)                                                                 | 0110                                     | 1100                          | 1101                                      | 1                                       | 00                                                      | 0110                        |

| ► Nd 5(24)                                                                 | 010                                      | ć                             |                                           | 010                                     |                                                         |                             |

| ▶ 🔣 N(31.0)                                                                | 00000000000                              | 0                             | 000                                       | 000000000000000000000000000000000000000 | 00100                                                   |                             |

|                                                                            |                                          |                               |                                           |                                         |                                                         |                             |

|                                                                            |                                          |                               |                                           |                                         |                                                         |                             |

|                                                                            |                                          |                               |                                           |                                         |                                                         |                             |

| 1                                                                          |                                          |                               |                                           |                                         |                                                         |                             |

| F                                                                          | iguro                                    | 0. <u>4</u> .bi               | it mult                                   | tinlior                                 | output                                                  | +                           |

| F                                                                          | igure                                    | 9: 4-bi                       | it mul                                    | tiplier                                 | output                                                  | t                           |

| F                                                                          | igure                                    | 9: 4-bi                       | it mul                                    | tiplier                                 | output                                                  |                             |

| F                                                                          | igure                                    | 9: 4-bi                       | it mul                                    | tiplier                                 | output                                                  |                             |

|                                                                            |                                          |                               |                                           | -                                       | _                                                       | 100.1                       |

| Name                                                                       | Value                                    | 0 ns                          | 20 na                                     | 0ni                                     | 50 /rs                                                  | 100.1<br>80.ns              |

|                                                                            |                                          |                               |                                           | -                                       | 50 /rs                                                  | <u>1000</u>                 |

| Name                                                                       | Value                                    | 0 ns                          | 20 na                                     | 0ni                                     | 50 /rs                                                  | 100.1<br>80.ns              |

| Name<br>• 🙀 19720                                                          | Value<br>00070100                        | 0 ns<br>(00001100             | 20 ns                                     | 0 ni                                    | 50 hs<br>10 hs<br>10 hs<br>11 h<br>11 h<br>11 h<br>11 h | 80 ns<br>00000200           |

| Name<br>• 🙀 197-0)<br>• 📷 4(3:0)                                           | Value<br>00000100<br>1100                | 0 ns<br>( 000011300<br>( 1100 | 20 ns 4<br>00001101 1                     | 0 ns<br>0000<br>1100                    | 50 hs<br>10 hs<br>10 hs<br>11 h<br>11 h<br>11 h<br>11 h | 80 ns<br>0 00000100<br>1100 |

| Name                                                                       | Value<br>00000100<br>1100<br>0110        | 0 ns<br>( 000011300<br>( 1100 | 20 ns 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0 ns<br>00000<br>1100<br>10             | 50 ns.<br>1900<br>1110<br>10                            | 80 ns<br>0 00000100<br>1100 |

| Name<br>• 100/ (P(7-0)<br>• 100/ A(3-0)<br>• 100/ (S(2-0)<br>• 100/ S(2-0) | Value<br>00000300<br>1100<br>0110<br>100 | 0 ns<br>( 000011300<br>( 1100 | 20 ns 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0ns<br>0000<br>1100<br>100<br>100       | 50 ns.<br>1900<br>1110<br>10                            | 80 ns<br>0 00000100<br>1100 |

| Name<br>• 100/ (P(7-0)<br>• 100/ A(3-0)<br>• 100/ (S(2-0)<br>• 100/ S(2-0) | Value<br>00000300<br>1100<br>0110<br>100 | 0 ns<br>( 000011300<br>( 1100 | 20 ns 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 0ns<br>0000<br>1100<br>100<br>100       | 50 ns.<br>1900<br>1110<br>10                            | 80 ns<br>0 00000100<br>1100 |

**Figure10: Peres And**

| Name      | Value     | pre      | 20 ns     | 40 ms                  | 60 ns    | 180 ns |

|-----------|-----------|----------|-----------|------------------------|----------|--------|

| - X120    | 00001100  | 00001100 | 00001111  | 50001100               | 00001115 |        |

| A30       | 1100      | 1100     | X IIII    | 1100                   | 1110     | 1100   |

| 1.685     | 1000      | 1100     | X 1101    | ( ic                   | 03       | X 0110 |

| - j \$200 | 101       |          |           | 101                    |          |        |

| A NULLA   | 000000000 | (        | 100100010 | 0100010001000100010010 |          |        |

Figure11: Peres Or

Figure12:Fredkin Nand

| Name              | Value         | Dris .   | 20 ns    | Hons                  | 60 ns   | 80 rs |

|-------------------|---------------|----------|----------|-----------------------|---------|-------|

| ▶ 📲 P(7.0)        | 11110001      | 11110011 | 11110000 | 11110011              | 111     | 12001 |

| A(3.0)            | 1100          | 1100     | 1111     | 1100                  | 1 110   | 1100  |

| ▶ 🔰 B[3:0]        | 0110          | 1100     | 1101     | k                     | 1000    | 0110  |

| ▶ <b>₩</b> \$[20] | 111           | 2        |          | 111                   |         |       |

| ▶ 駴 N(31:0)       | 0000000000000 |          | 000      | 101000100010001000100 | 0000000 |       |

# Figure13:Fredkin Nor

| 🕨 🙀 P[7:0] 241       | 24 | V in 1 |       |    |     |    |     |     |

|----------------------|----|--------|-------|----|-----|----|-----|-----|

| 2 22002330 St        |    |        | 95    | 6  | 4   | 14 | 251 | 241 |

| 🕨 😽 A[Bil] 12        | 12 | 15     | )( 12 | 14 | X   |    | 12  |     |

| <b>▶ 👹 8</b> (3,0) 6 | 12 | 13     |       |    |     |    | 6   |     |

| 🕨 👹 S(24) 👘 🕇        | 1  | 1      | 2     | 3  | X 4 | 5  | 6   |     |

| 🕨 👹 NIBEN) 🕴 4       |    |        |       |    | 4   |    |     |     |

## **Figure14: ALU Simulation output**

Figure 14 represents the simulation output of 4-bit ALU, for various combinations of the input data resultant arthematic and logical outputs are generated based on the selection combinations.

| Device Utilization Summary (estimated values) |      |           |             |  |  |  |

|-----------------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |  |  |  |

| Number of Slice LUTs                          | 2151 | 63400     | 3%          |  |  |  |

| Number of fully used LUT-FF pairs             | 0    | 2151      | 0%          |  |  |  |

| Number of bonded IOBs                         | 131  | 210       | 62%         |  |  |  |

## **Figure 15: Design Summary**

Figure 8 represents the design summary; from this it is observed that the proposed Reversible ALU consumes the less area, lessLUTs.

Figure 9 represents the Time summary, from this it is observed that the proposed Reversible ALU consumes the less time with less logical delay and route delay.

Table 2: Performance Comparison

| Parameter              | CM<br>OS<br>ALU | Reversi<br>ble ALU | %impro<br>ved            |

|------------------------|-----------------|--------------------|--------------------------|

| LUTS                   | 2682            | 2152               | 19.7614<br>%<br>decrease |

| Delay(ns)              | 39.5<br>57      | 26.859             | 32.1005<br>%<br>decrease |

| Adders/subtr<br>actors | 60              | 0                  | NA                       |

| Xors                   | 1947            | 6637               | NA                       |

| BELS                   | 3427            | 2182               | 36.3292<br>%<br>decrease |

| LUT2 | 418 | 508 | 21.5311  |

|------|-----|-----|----------|

|      |     |     | %        |

|      |     |     | increase |

|      |     |     |          |

| LUT3           | 312        | 43          | 86.2179       |

|----------------|------------|-------------|---------------|

|                |            |             |               |

| LUT4           | 301        | 469         | 55.814%       |

|                |            |             | increase      |

| E10175Table 2, | <b>390</b> | c105n4clude | tch0at5t1h2e8 |

|                |            |             | %             |

|                |            |             | decrease      |

| LUT6           | 1261       | 977         | 22.5218       |

|                |            |             | %             |

|                |            |             | decrease      |

| MUXF7          | 34         | 31          | 8.82353       |

|                |            |             | %             |

|                |            |             | decrease      |

|                |            |             |               |

|                |            |             |               |

|                |            |             |               |

proposed RALU consumes the less area with respect to XORs, LUTs and it also consumes the less delay as compared to the conventional CMOS ALU respectively.

# FPGA IMPLEMENTATION

Figure 16: FPGA IMPLEMENTATION OFRFA

In n-bit reversible full adder when a[0:4]=1

B[0:4]=1; cin=[1] then sum[0:4]=1; Cout=1

Figure 17: FPGA IMPLEMENTATION OFRFA

In n-bit reversible full adder when a[0:4]=1 B[0:4]=1;cin=[0] then sum[0]=0,sum[1:4]=1; Cout=1

# Figure 18: FPGA IMPLEMENTATION OFR-ALU MULTIPLIER

In alu 4-bit multipler If a=0 b=0 and selection line=111 then output=11111

**Figure 19: FPGA IMPLEMENTATION OFR-ALU MULTIPLIER** In alu 4-bit multipler If a=00011 b=00001 and selection line=101Then output=00011

## Conclusion

In this paper an area efficient reversible full adder was designed, utilizing this full adder an 4-bit ripple carry adder was developed. And utilizing this 4-bit RCA and fredkin gate an 4-bit array multiplier was developed. Finally common architecture for both adder and subtractor has developed, using this adder-subtractor, array multiplier and fredkin gate an 4-bit ALU has design with low hardware resources utilization. The simulation and synthesis results shows the proposed method has area, power and delay efficient compared to this state of art Approaches and many literatures. This workcan be extended to implement the N-bit sequential logical units such as shift register, counters and so on thus they can be effectively used in every DSP processor and design of any IC achieved through low power ,low delay and area efficient.

## REFERENCES

- Zulehner, Alwin, and Robert Wille. "One- pass design of reversible circuits: Combining embedding and synthesis for reversible logic." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 37.5 (2017): 996-1008. [2]Raveendran, Sithara, et al. "Design and Implementation of Reversible Logic basedRGB to Gray scale Color Space Converter." TENCON 2018-2018 IEEE Region 10 Conference. IEEE, 2018.

- 2. Qian, Junzhou, and Junchao Wang. "A 4- bit array multiplier design by reversible logic." *Information Technology*. CRC Press, 2015. 21-24.

- Ghosh, Arpita, and S. K. Sarkar. "Performance Investigation of Nanoscale Reversible Logic gates designed with SE- TLG Approach." *International Journal of Electronics* just-accepted (2020).

- 4. Gaur, Hari Mohan, Ashutosh Kumar Singh, and Umesh Ghanekar. "In-depth comparative analysis of reversible gates for designing logic circuits." Procedia ComputerScience 125 (2018): 810-817.

- 5. Sasamal, Trailokya Nath, Ashutosh Kumar Singh, and Anand Mohan.

- 6. "Reversible logic circuit synthesis and optimization using adaptive genetic algorithm." *Procedia Computer Science* 70 (2015): 407-413.

- Ahmad, Peer Zahoor, et al. "A novel reversible logic gate and its systematic approach to implement cost-efficient arithmetic logic circuits using QCA." *Data in brief* 15 (2017): 701-708.

8. Yugandhar, K., et al. "High Performance Array Multiplier using Reversible Logic Structure." 2018 International Conference on Current Trends towards Converging Technologies (ICCTCT). IEEE, 2018. [9]Kamaraj, A., and P. Marichamy. "Design of integrated reversible fault-tolerant arithmetic and logic unit." Microprocessors and Microsystems 69 (2019): 16-23. [10]Amirthalakshmi, S.Selvakumar Raja. "Design and analysis of low T. М., and power 8-bit ALU on reversible logic fornanoprocessors." Journal of *AmbientIntelligence* and Humanized Computing (2018): 1-19.